Multivibrator (Sistem Digital)

SISTEM DIGITAL

BAB IX

MULTIVIBRATOR

Konsep Dasar Multivibrator

Indikator Multivibrator

Konsep Dasar Multivibrator

Karakteristik Multivibrator

Fungsi Multivibrator

1. Sebagai Timer Clock dalam microcontroller

2. Pembangkit gelombang dasar dalam teknik digital

3. Pembentuk gelombang dalam teknik pembuatan PWM(Pulse Wave Modulation)

4. Memori dalam teknik computer (sebagai contoh, dalam teknik computer dewasa ini dalam satu Microchip berukuran 3 cm x 3 cm terdapat kurang lebih 200 miliar multivibrator)

Jenis-jenis Multivibrator

1. Multivibrator astabil (astable multivibrator)

2. Multivibrator monostabil (monostable multivibrator)

3. Multivibrator bistabil (bistable multivibrator)

Multivibrator Astabil

Multivibrator Monostabil

Karakteristik Multivibrator

Aplikasi Multivibrator

Multivibrator astabil

1. Sebagai pembangkit sinyal yang menghasilkan gelombang keluaran dengan periode tetap.

2. Sebagai rangkaian pembangkit denyut lonceng(clock pulse)untuk rangkaian pencacah(counter), penghitung waktu(timer), modulator dan rangkaian logika digital lainnya.

Multivibrator monostabil

1. Peregangan periode waktu terhadap denyut sinyal keluaran(pulsestretching).

2. Sebagai rangkaian pendeteksi ujung jatuh pada denyut rangkaian flip-flop.

Multivibrator bistabil

1. Membangkitkan dan memproses sinyal-sinyal denyut.

2. Melakukan operasi-operasi seperti penyimpanan bit data dan operasi logika(aljabar Boole)

3. Pembentuk sistem memori dalam bentuk flip-flop RS atau JK.

Sumber : http://hendrototok.blogspot.com/2015/12/multivibrator-sistem-digital.html

1. RS FLIP-FLOP

BAB IX

MULTIVIBRATOR

Konsep Dasar Multivibrator

Multivibrator adalah rangkaian elektronik terpadu yang digunakan untuk menerapkan variasi dari sistem dua keadaan (two state system) yang dapat menghasilkan suatu sinyal kontinu, yang dapat digunakan sebagai pewaktu (timer) dari rangkaian-rangkaian sekuensial.

Indikator Multivibrator

Indikator munculnya gelombang kotak tersebut dapat dilihat pada menyalanya LED yang bergantian, saat ON (ada tegangan, maka LED menyala), saat OFF (tidak ada tegangan, maka LED padam).

Konsep Dasar Multivibrator

1. Multivibrator beroperasi sebagai osilator, yaitu sebagai sebuah rangkaian pembangkit sinyal, di mana sinyal yang dihasilkan pada keluaran akan berbentuk gelombang persegi (square wave).

2. Multivibrator dalam pengoperasiannya memiliki dua keadaan utama, yaitu keadaan stabil dan keadaan tak stabil.

Karakteristik Multivibrator

1. Keadaan stabil adalah keadaan di mana taraf amplitudo sinyal keluaran adalah tetap / stagnan pada suatu nilai tertentu.

2. Keadaan tak stabil adalah keadaan di mana taraf ampiltudo sinyal selalu berubah-ubah mengikuti denyut tegangan pada komponen aktif.

3. Keadaan tak stabil di pengaruhi oleh waktu laju pengisian / pengosongan kapasitor yang besarnya ditentukan dari kapasitas kapasitor.

4. Rangkaian multivibrator terdiri dari komponen penguat aktif yang di kopel silang dengan komponen-komponen pasif (resistor dan kapasitor).

5. Fungsi resistor pada rangkaian multivibrator adalah sebagai sumber arus bagi pengisian muatan kapasitor, sedangkan kapasitor berfungsi sebagai kopel yang akan menentukan besar tegangan dari komponen penguat yang aktif.

1. Sebagai Timer Clock dalam microcontroller

2. Pembangkit gelombang dasar dalam teknik digital

3. Pembentuk gelombang dalam teknik pembuatan PWM(Pulse Wave Modulation)

4. Memori dalam teknik computer (sebagai contoh, dalam teknik computer dewasa ini dalam satu Microchip berukuran 3 cm x 3 cm terdapat kurang lebih 200 miliar multivibrator)

Jenis-jenis Multivibrator

1. Multivibrator astabil (astable multivibrator)

2. Multivibrator monostabil (monostable multivibrator)

3. Multivibrator bistabil (bistable multivibrator)

Multivibrator Astabil

1. Multivibrator astabil adalah multivibrator yang bersifat free-running, yaitu tidak memiliki keadaan stabil yang permanen pada suatu periode tertentu, oleh sebab itu tidak dibutuhkan suatu masukan(input).

2. Waktu aktif dari setiap komponen penguat bergantung pada waktu pengisian dan pengosongan kapasitor pada rangkaian.

Multivibrator Monostabil

- Multivibrator monostabil adalah multivibrator yang memiliki satu kondisi stabil dan satu kondisi tak stabil.

- Mempunyai satu buah masukan denyut pemicu(input trigger pulse) untuk mengubah keadaan stabil dan tak stabil.

- Keadaan stabil akan menjadi tak stabil apabila di berikan suatu denyut pemicu negatif(negative trigger pulse)pada komponen penguat yang sedang aktif.

- Jika suatu denyut masukan berulang-ulang yang diterapkan pada rangkaian dapat mempertahankan kondisi tak stabil, maka rangkaian tersebut disebut retriggerable monostable.

- Sebaliknya jika suatu denyut masukan berulang-ulang yang di terapkan pada rangkaian tidak mempengaruhi periode kondisi tak stabil, maka rangkaian tersebut di sebut nonretriggerable monostable.

Karakteristik Multivibrator

a. Tidak menggunakan kapasitor sehingga pada awal rangkaian diaktifkan komponen penguat berada pada daerah aktif.

b. Pengubahan keadaan dari sinyal keluaran dilakukan dengan menerapkan masukan“set”dan“reset”pada komponen penguat yang aktif. Jika di berikan masukan pada salah satu terminal tersebut, maka keadaan keluaran akan berubah ke taraf ke balikan dari keadaan awal.

Aplikasi Multivibrator

Multivibrator astabil

1. Sebagai pembangkit sinyal yang menghasilkan gelombang keluaran dengan periode tetap.

2. Sebagai rangkaian pembangkit denyut lonceng(clock pulse)untuk rangkaian pencacah(counter), penghitung waktu(timer), modulator dan rangkaian logika digital lainnya.

Multivibrator monostabil

1. Peregangan periode waktu terhadap denyut sinyal keluaran(pulsestretching).

2. Sebagai rangkaian pendeteksi ujung jatuh pada denyut rangkaian flip-flop.

Multivibrator bistabil

1. Membangkitkan dan memproses sinyal-sinyal denyut.

2. Melakukan operasi-operasi seperti penyimpanan bit data dan operasi logika(aljabar Boole)

3. Pembentuk sistem memori dalam bentuk flip-flop RS atau JK.

Sumber : http://hendrototok.blogspot.com/2015/12/multivibrator-sistem-digital.html

Rangkaian Logika Sekuensial (Sistem Digital)

Ilmu MahasiswaNovember 21, 2019

SISTEM DIGITAL

BAB VII

BAB VII

RANGKAIAN LOGIKA SEKUENSIAL

Pada rangkaian logika sekuensial, keadaan keluaran selainditentukan oleh keadaan masukan juga ditentukan olehkeadaan keluaran sebelumnya. Hal itu menunjukkan bahwarangkaian logika sekuensial harus mempunyai pengingat (memory), atau kemampuan untuk menyimpan informasi.Rangkaian dasar yang dapat dipakai untuk membentukrangkaian logika sekuensial adalah latch dan flip-flop.Perbedaan latch dan flip-flop terletak pada masukanclock. Pada flip-flop dilengkapi dengan masukan clock,sedangkan pada latch tidak. Flip-flop hanya akan bekerjapada saat transisi pulsa clock dari tinggi ke rendah ataudari rendah ke tinggi, tergantung dari jenis clock yangdigunakan. Transisi pulsa clock dari rendah ke tinggi disebut transisi positif, sedangkan transisi tinggi kerendah di sebut transisi negatif.

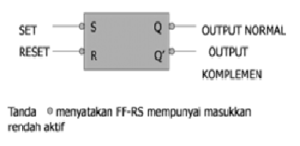

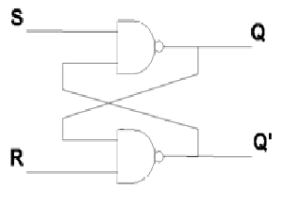

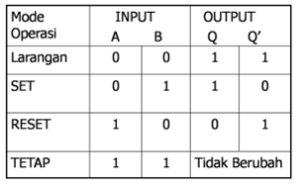

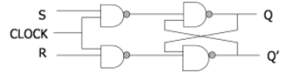

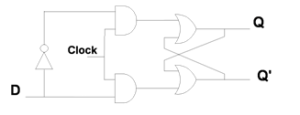

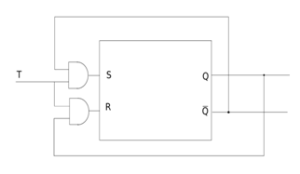

1. RS FLIP-FLOP

Flip-flop RS atau SR (Set-Reset) merupakan dasar dari flip-flop jenis lain. Flip-flop ini mempunyai 2 masukan: satu disebut S (SET) yang dipakai untuk menyetel (membuat keluaran flip-flop berkeadaan 1) dan yang lain disebut R (RESET) yang dipakai untuk me-reset (membuat keluaran berkeadaan 0).

a. FF-RS (dirangkai dari NAND gate)

Rangkaian Logika FF-RS

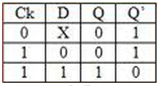

Tabel Kebenaran FF RS

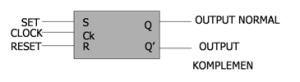

b. FF – RS Berdetak

Dengan adanya detak akan membuat FF-RS bekerja sinkron atau aktif HIGH

Simbol Logika

Rangkaian Logika FF-RS Berdetak

Tabel Kebenaran FF-RS Berdetak

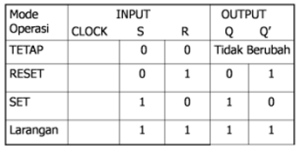

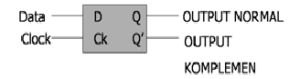

2. D FLIP-FLOP

Sebuah masalah yang terjadi pada Flip-flop RS adalah dimana keadaan R = 1, S = 1 harus dihindarkan. Satu cara untuk mengatasinya adalah dengan mengizinkan hanya sebuah input saja dimana FF-D mampu mengatasi masalah tersebut

Simbol Logika

Rangkaian Logika

Tabel Kebenaran

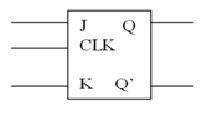

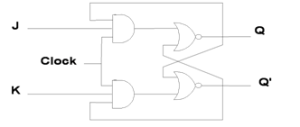

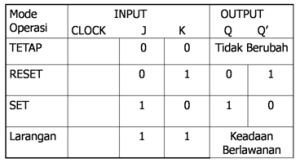

3. JK FLIP-FLOP

FF JK mempunyai masukan “J” dan “K”. FF ini “dipicu” oleh suatu pinggiran pulsa clock positif atau negatif. FF JK merupakan rangkaian dasar untuk menyusun sebuah pencacah. FF JK dibangun dari rangkaian dasar FF SR dengan menambahkan dua gerbang AND pada masukan R dan S serta dilengkapi dengan rangkaian diferensiator pembentuk denyut pulsa clock

Simbol logika

Rangkaian Logika

Tabel Kebenaran

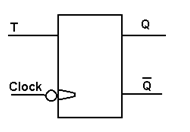

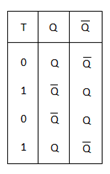

4. T FLIP-FLOP

Nama flip-flop T diambil dari sifatnya yang selalu berubah keadaan setiap ada sinyal pemicu (trigger) pada masukannya. Input T merupakan satu-satunya masukan yang ada pada flip-flop jenis ini sedangkan keluarannya tetap dua, seperti semua flip-flop pada umumnya. Kalau keadaan keluaran flip-flop 0, maka setelah adanya sinyal pemicu keadaan-berikut menjadi 1 dan bila keadaannya 1, maka setelah adanya pemicuan keadaannya berubah menjadi 0. Karena sifat ini sering juga flip-flop ini disebut sebagai flip-flop toggle (berasal dari scalar toggle/pasak).

Simbol Logika

Rangkaian Logika

Tabel Kebenaran

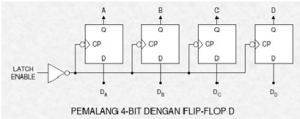

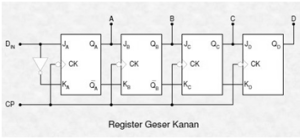

5. REGISTER

Register adalah himpunan dari sejumlah sel yang masing-masing terdiri dari sebuah flip-flop, dimana setiap sel dapat menyimpan data sebanyak 1-bit. Register ini umumnya dapat dibaca dan ditulis sehingga berfungsi sebagai memori yang berukuran kecil. Fungsi dari register kadang-kadang lebih dari hanya sekedar menyimpan data, tetapi dapat juga mengolahnya secara terbatas, misalnya menggeser kekiri atau kekanan.

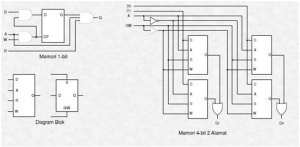

Register Pemalang (Latch)

Disebut pemalang karena register ini berfungsi untuk memalang data. Artinya nilai data yang menjadi masukannya akan dipertahankan pada keluarannya, walaupun masukan tersebut telah dihilangkan. Register ini sangat diperlukan untuk menghubungkan peralatan berkecepatan tinggi dengan yang berkecepatan rendah. Dalam hal ini register berfungsi sebagai penyangga (buffer). Pemalang umumnya dibentuk dengan menggunakan flip-flop D.

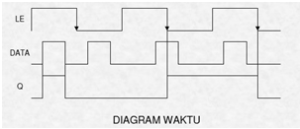

Jika masukan LE (Latch Enable) tinggi maka semua flip-flop mendapat pulsa clock sehingga menangkap data masukannya. Selanjutnya jika data masukan dihilangkan maka nilai data sebelumnya akan tetap ada pada keluaran register. Data ini akan tetap dipertahankan sampai ada pengambilan data yang baru.

Pemalang Transparan

Pemalang umumnya dibuat transparan dimana masukan LE bersifat level sensitive. Jika LE bernilai tinggi maka nilai keluaran flip-flop yang bersangkutan akan sama dengan nilai keluarannya. Saat LE beralih ke rendah maka nilai masukan pada saat itu akan ditangkap dan dipertahankan.

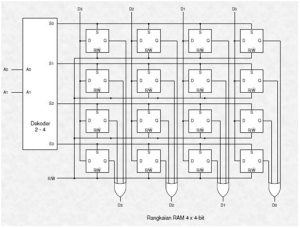

Memori

Memori berfungsi untuk menyimpan informasi. Jumlah data yang dapat disimpan tergantung kapasitas memori tersebut. Ada memori yang hanya dapat dibaca (ROM) ada pula yang dapat dibaca dan ditulis (RAM)

Register Geser Kanan

Pada register ini flip-flop yang dikanan mendapat masukan dari keluaran flip-flop yang dikiri.

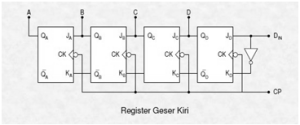

Register Geser Kiri

Pada register ini flip-flop yang dikiri mendapat masukan dari keluaran flip-flop yang dikanan.

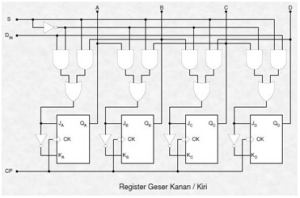

Register Geser Kanan / Kiri

Masukan suatu flip-flop bisa dari flip-flop yang dikiri ataupun yang dikanannya, tergantung pada nilai logika masukan S (select).

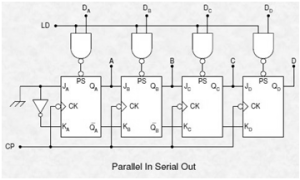

Parallel Input Serial Output

Data untuk masing-masing flip-flop akan di-loading pada saat masukan LD (load) berlogika tinggi. Selanjutnya data akan digeser kekanan pada setiap pulsa CP.

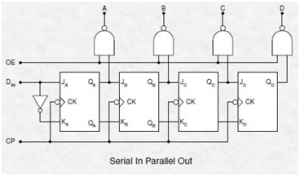

Serial Input Parallel Output

Data untuk masing-masing flip-flop akan dikeluarkan pada saat masukan OE (output enable) berlogika tinggi.

Aljabar Boole dan Peta Kernaugh (Sistem Digital)

Ilmu MahasiswaNovember 21, 2019

SISTEM DIGITAL

Kedua rangkaian logika diatas memiliki keluaran yang sama untuk kondisi masukan A dan B yang sama. Sifat Reduksi A + AB = A Untuk membuktikan sifat atau teorema ini perhatikan persamaan berikut:

BAB V

ALJABAR BOOLE DAN PETA KERNAUGH

ALJABAR BOOLE

1.HUKUM KOMUNITATIF

1.1. Hukum Komunitatif Untuk Gerbang Logika AND

Hukum Komutatif Untuk Gerbang Logika AND Gerbang OR dengan 2 masukan tertentu, yaitu A dan B, dapat dipertukarkan tempatnya dan dapat merubah urutan sinyal-sinyal masukan. Perubahan tersebut tidak akan mempengaruhi keluarannya. Dalam hukum persamaan Boolean hal ini dapat ditulis sebagai berikut : A . B = B . A = Y

1.2. Hukum Komutatif Untuk Gerbang Logika OR

Hukum komutatif aljabar boolean memiliki kesamaan degan aljabar biasa. Berikut ini akan kita lihat pemakaian hukum komutatif dalam gerbang-gerbang logika Hukum Komutatif Untuk Gerbang Logika OR Gerbang OR dengan 2 masukan tertentu, yaitu A dan B, dapat dipertukarkan tempatnya dan dapat merubah urutan sinyal-sinyal masukan. Perubahan tersebut tidak akan mempengaruhi Dalam hukum persamaan Boolean hal ini dapat ditulis sebagai berikut : A + B = B + A = Y

2.HUKUM ASOSIATIF

2.1. Hukum Asosiatif Untuk gerbang OR

Hukum Asosiatif untuk Gerbang Logika OR Gerbang OR dengan 2 masukan tertentu, yaitu A dan B, dapat dikelompokan tempatnya dan diubah urutan sinyal-sinyal masukannya. Perubahan tersebut tidak akan mengubah keluarannya. Dalam hukum persamaan Boolean ditulis sebagai berikut: A + ( B+ C) = ( A + B ) + C Pada hakekatnya cara pengelompokan variabel dalam suatu operasi OR tidak berpengaruh pada keluarannya. Artinya keluarannya akan tetap sama dengan : Y = A + B + C Perhatikan gambar berikut

Hukum Asosiatif untuk Gerbang Logika AND Gerbang AND dengan 2 masukan yaitu yaitu A dan B, dapat dikelompokan tempatnya dan diubah urutan sinyal-sinyal masukannya. Perubahan tersebut tidak akan mengubah keluarannya. Dalam hukum persamaan Boolean ditulis sebagai berikut: A. (B . C ) = ( A . B ) .C = Y

3.HUKUM DISTRIBUTIF

Gerbang AND dan OR dengan masukan tertentu, yaitu A, B¸dan C, dapat disebarkan tempatnya, dan dapat dirubah urutan-urutan sinyal-sinyal masukannya. Perubahan tersebut tidak akan mengubah keluarannya. Dalam persamaan boolean ditulis sebagai berikut : A. ( B + C ) = AB + AC

Sifat-sifat Khusus Aljabar Boole

Sifat Khusus dalam operasi Gerbang OR

– Kaidah Pertama : A + 0 = A

– Kaidah Kedua : A + 1 = 1

– Kaidah Ketiga : A + A = A

– Kaidah Keempat :A+Anot=

Sifat Khusus dalam operasi Gerbang AND – Kaidah Pertama : A . 0 = 0

– Kaidah Kedua : A.1 = A

– Kaidah Ketiga : A . A = A

– Kaidah Keempat : A . ?

Sifat Absorpsi

Untuk membuktikan sifat atau teorema ini perhatikan persamaan berikut :

Kedua rangkaian logika diatas memiliki keluaran yang sama untuk kondisi masukan A dan B yang sama. Sifat Reduksi A + AB = A Untuk membuktikan sifat atau teorema ini perhatikan persamaan berikut:

Sifat Absorpsi

Untuk membuktikan sifat atau teorema ini perhatikan persamaan berikut :

Teorema De Morgan – Teorema Pertama

Persamaan gerbang logika NOR :

Rangkaian logika 2 masukan yang di “NOT” kan dan kemudian hubungkan ke gerbang AND

Dari rangkaian diatas dapat ditulis persamaan aljabar boolean sebagai berikut :

Karena kedua rangkaian diatas menghasilkan masukan dan keluaran yang ekivalen atau sama maka dapat dinyatakan sebagai berikut :

Teorema Kedua

Persamaan gerbang logika NAND :

Rangkaian yang terdiri dari logika NOT dan gerbang logika OR :

Rangkaian diatas dapat dituliskan ke dalam persaman berikut :

Kedua rangkaian logika diatas memiliki kesamaan sifat atau dapat dikatakan keduanya ekivalen sehingga dapat dibuktikan teorema de morgan sesuai dengan kedua persamaan di atas.

PETA KARNAUGH

Peta Karnaugh digunakan sebagai cara untuk menyederhanakan persamaan logika secara grafis, atau dapat pula dipandang sebagai metoda untuk mengubah suatu tabel kebenaran ke rangkaian logika yang sesuai secara sederhana dan rapi.

Peta Karnaugh untuk 2 variabel

Peta Karnaugh untuk 3 variabel

Peta karnaugh untuk 4 variabel

PENYEDERHANAAN DENGAN KARNAUGH MAP

Karnaugh Map adalah pengganti persamaan aljabar boole.Maksud penulisan variable pada peta (map) ini, agar dalam peta hanya ada satu variable yang berubah dari bentuk komplemen menjadi bentuk bukan komplemen

1. PENGELOMPOKAN NILAI VARIABEL (LITERAL)

– Pasangan(Pairs)

Adalah suatu pasangan nilai angka 1yang saling berdekatan dalam arah horizontal atau vertikal.Jika dalam sebuah peta karnaugh terdapat lebih dari satu pasangan, kita dapat melakukan operasi OR pada hasil kali yang telah disederhanakan itu, untuk memperoleh persamaan boole

-Kuad

Adalah kelompok yang terdiri dari empatbuah nilai angka 1 yang tersusun berdampingan dari ujung ke ujung. “Bila kita menjumpai suatu susunan kuad, maka lingkarilah kelompok itu, karenahal ini dapat menyederhanakan bentuk hasil kali semula. Dalam kenyataan, kehadiran sebuah kuad berarti terhapusnya dua variable beserta komplemennya dari persamaan boole.”

-Oktet

Adalah kelompok yang terdiri daridelapannilai angka 1 yangberdampingan. “Sebuah oktet selalu berarti penghapusan tiga buah variabel dan komponen-komponennya dari persamaan boole yang bersangkutan.”

Disederhanakan menjadi :

Kesimpulan : “ Dalam menyederhanakan persamaan boole, kita harus melakukan Identifikasi mulai dengan melingkari oktet, Kuad atau pasangan angka dari masing-masing dapat menghapuskan tiga, dua atau satu variabel.”

2.KELOMPOK KELEBIHAN (REDUNDANT)

Terdapat kelompok angka 1 ditengah yang perlu diperiksa, ternyata tumpang tindih baik angka 1 disebelah kiri ataupun disebelah kanan disebut pasangan Kelebihan dan harus dihapuskan agar diperoleh peta yang baik sederhana, yaitu sebagai berikut :

3. KEADAAN TIDAK PEDULI ( DON’T CARE )

Adalah dinyatakan dengan tanda x (tidak terjadi perubahan apapun pada keluaran, walaupun nilai masukan diubah) dan x dapat berupa nilai 0 atau 1.

4. PENGGULUNGAN PETA

Karena persamaan bolle di atas dihindarkan,karena masih dapat disederhanakan, maka pengeompokan angka 1 menggunakan cara penggulunganyaitu dalam bentuk Kuaddan dalam peta sebagai berikut :

0 comments:

Post a Comment